UNIT II: Microprocessor Architecture 8086: 8086 basic block diagram, Internal Microprocessor Architecture,

Real Mode Memory Addressing, Registers, pin configuration, segmentation. Data Movement Instructions: MOV,

PUSH/POP, Load-Effective Address, String Data Transfers, Miscellaneous Data Transfer Instructions, Segment

Override Prefix, Assembler Details. Arithmetic and Logic Instructions: Addition, Subtraction and Comparison,

Multiplication and Division, BCD and ASCII Arithmetic, Basic Logic Instructions, Shift and Rotate, String

Comparisons. Program Control Instructions: The Jump Group, Controlling the Flow of the Program, Procedures,

and Introduction to Interrupts, Machine Control and Miscellaneous Instructions. Assembler directives, assembler

instructions, Assembly Language Programming.

Syllabus Source:

https://csvtu.ac.in/ew/download/b-tech-5th-semester-5/?wpdmdl=14364&refresh=63c24614a8a6f1673676308

👉Prerequisite: Study these Topics to answer the Questions

1. 8086 Basic Block diagram.

2. 8086 Pin configuration.

3. Memory Addressing

4. 8086 Instructions: for Instructions click on this 👉Notes8086Instruction

Hint: Types of Instructions in 8086

- Data Copy/Transfer instructions

- Arithmetic instructions.

- Logical instructions.

- Shift & Rotate instructions.

- Branch instructions.

- Loop instructions.

- Machine Control instructions.

- Flag Manipulation instructions.

- String instructions.

Questions: Compiled from Previous Year Question Paper:

Q1. Explain BIU & EU of 8086 microprocessor.

Ans:

BIU (Bus Interface Unit)

BIU takes care of all data and addresses transfers on the buses for the EU like sending addresses, fetching instructions from the memory, reading data from the ports and the memory as well as writing data to the ports and the memory.

It has the following functional parts −

Instruction queue − BIU contains the instruction queue. BIU gets upto 6 bytes of next instructions and stores them in the instruction queue.

Fetching the next instruction while the current instruction executes is called pipelining.

Segment register − BIU has 4 segment buses, i.e. CS, DS, SS& ES. It holds the addresses of instructions and data in memory, which are used by the processor to access memory locations. It also contains 1 pointer register IP, which holds the address of the next instruction to executed by the EU.

o CS − It stands for Code Segment. It is used for addressing a memory location in the code segment of the memory, where the executable program is stored.

o DS − It stands for Data Segment. It consists of data used by the program andis accessed in the data segment by an offset address or the content of other register that holds the offset address.

o SS − It stands for Stack Segment. It handles memory to store data and addresses during execution.

o ES − It stands for Extra Segment. ES is additional data segment, which is used by the string to hold the extra destination data.

Instruction pointer − It is a 16-bit register used to hold the address of the next instruction to be executed.

EU (Execution Unit) :

Execution unit gives instructions to BIU stating from where to fetch the data and then decode and execute those instructions. Its function is to control operations on data using the instruction decoder & ALU. EU has no direct connection with system buses as shown in the above figure, it performs operations over data through BIU.

Let us now discuss the functional parts of 8086 microprocessors.

ALU: It handles all arithmetic and logical operations, like +, −, ×, /, OR, AND, NOT operations.

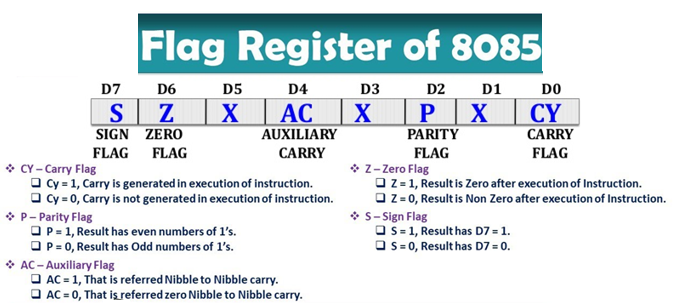

Flag Register: It is a 16-bit register that behaves like a flip-flop, i.e. it changes its status according to the result stored in the accumulator. It has 9 flags and they are divided into 2 groups − Conditional Flags and Control Flags. Conditional Flags It represents the result of the last arithmetic or logical instruction executed. Following is the list of conditional flags −

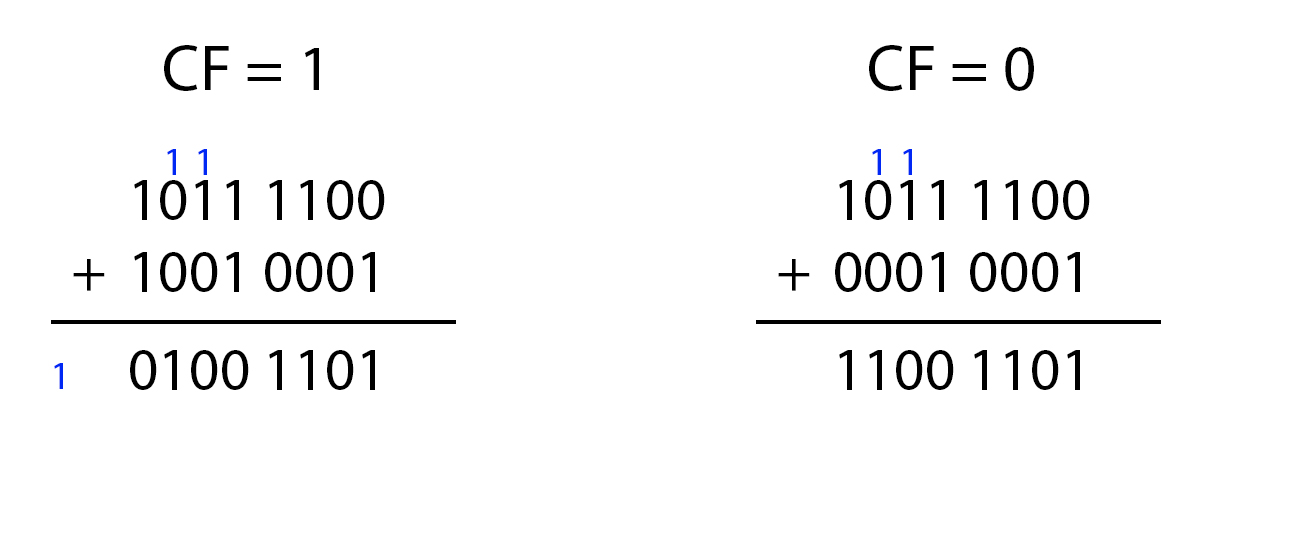

Carry flag − This flag indicates an overflow condition for arithmetic operations.

Auxiliary flag − When an operation is performed at ALU, it results in a carry/barrow from lower nibble (i.e. D0 – D3) to upper nibble (i.e. D4 – D7), then this flag is set, i.e. carry given by D3 bit to D4 is AF flag. The processor uses this flag to perform binary to BCD conversion.

Parity flag − This flag is used to indicate the parity of the result, i.e. when the lower order 8-bits of the result contains even number of 1’s, then the Parity Flag is set. For odd number of 1’s, the Parity Flag is reset.

Zero flag − This flag is set to 1 when the result of arithmetic or logical operation is zero else it is set to 0.

Sign flag − This flag holds the sign of the result, i.e. when the result of the operation is negative, then the sign flag is set to 1 else set to 0.

Overflow flag − This flag represents the result when the system capacity is exceeded. Control Flags Control flags controls the operations of the execution unit. Following is the list of control flags −

Trap flag − It is used for single step control and allows the user to execute one instruction at a time for debugging. If it is set, then the program can be run in a single step mode.

Interrupt flag − It is an interrupt enable/disable flag, i.e. used to allow/prohibit the interruption of a program. It is set to 1 for interrupt enabled condition and set to 0 for interrupt disabled condition.

Direction flag − It is used in string operation. As the name suggests when it is set then string bytes are accessed from the higher memory address to the lower memory address and vice-a-versa.

General purpose register:

There are 8 general purpose registers, i.e., AH, AL, BH, BL, CH, CL, DH, and DL. These registers can be used individually to store 8-bit data and can be used in pairs to store 16bit data. The valid register pairs are AH and AL, BH and BL, CH and CL, and DH and DL. It is referred to the AX, BX, CX, and DX respectively.

AX register − It is also known as accumulator register. It is used to store operands for arithmetic operations.

BX register − It is used as a base register. It is used to store the starting base address of the memory area within the data segment.

CX register − It is referred to as counter. It is used in loop instruction to store the loop counter.

DX register − This register is used to hold I/O port address for I/O instruction.

Q2. Explain the various addressing modes of 8086 with suitable example.

Ans : click👉 Addressing modes of 8086

Types of addressing mode in 8086

- Immediate addressing mode: MOV

AX,10ABH

- Direct addressing mode: MOV AX,

[5000H]

- Register addressing mode: MOV

AX,BX

- Register Indirect addressing

mode: MOV AX,[BX]

- Indexed addressing mode: MOV

AX,[SI]

- Register relative addressing

mode: MOV AX, 50H[BX]

- Base plus index addressing mode:

MOV AX, [BX] [SI]

- Base relative plus index

addressing mode: MOV AX,50H[BX][SI]

Q3. Explain the following instructions:

(i) XCHG

(ii) CLD

(iii) AAA

(iv)CMPS

Answer: Click on this 👉📝Q3#Notes

Q4. WAP to find the smallest number among a string of 10 data bytes starting from location 2000H: 3000H and store the result in 2000H: 0500H.

For any further updates , Please visit this page on Regular Interval

Images may be subject to copyright

~Pradeep Kumar